English

English  Español

Español Português

Português русский

русский Français

Français 日本語

日本語 Deutsch

Deutsch tiếng Việt

tiếng Việt Italiano

Italiano Nederlands

Nederlands ภาษาไทย

ภาษาไทย Polski

Polski 한국어

한국어 Svenska

Svenska magyar

magyar Malay

Malay বাংলা ভাষার

বাংলা ভাষার Dansk

Dansk Suomi

Suomi हिन्दी

हिन्दी Pilipino

Pilipino Türkçe

Türkçe Gaeilge

Gaeilge العربية

العربية Indonesia

Indonesia Norsk

Norsk تمل

تمل český

český ελληνικά

ελληνικά український

український Javanese

Javanese فارسی

فارسی தமிழ்

தமிழ் తెలుగు

తెలుగు नेपाली

नेपाली Burmese

Burmese български

български ລາວ

ລາວ Latine

Latine Қазақша

Қазақша Euskal

Euskal Azərbaycan

Azərbaycan Slovenský jazyk

Slovenský jazyk Македонски

Македонски Lietuvos

Lietuvos Eesti Keel

Eesti Keel Română

Română Slovenski

Slovenski

Bagaimanakah IC Cip Boleh Mengurangkan Risiko dalam Binaan Elektronik Anda Seterusnya?

Abstrak

A IC cip selalunya merupakan item terkecil pada bil bahan, namun ia boleh menjadi punca kelewatan terbesar, kegagalan medan dan kos tersembunyi. Jika anda pernah berurusan dengan produk "berfungsi di makmal, gagal di dunia nyata", penggantian komponen mengejutkan atau notis tamat hayat secara tiba-tiba, anda sudah tahu betapa cepatnya projek boleh berputar.

Artikel ini menguraikan cara praktikal untuk memilih, mengesahkan dan menyepadukan aIC cipjadi produk anda stabil dalam pengeluaran—bukan hanya dalam prototaip. Anda akan mendapat senarai semak yang jelas untuk pemilihan, pagar kebolehpercayaan, aliran kerja pengesahan mudah untuk mengelakkan pemalsuan, dan pendekatan yang berfikiran pembuatan untuk penyepaduan PCBA. Sepanjang perjalanan, saya akan berkongsi cara pasukan biasanya menyelesaikan masalah ini dengan sokongan daripadaShenzhen Greeting Electronics Co., Ltd., terutamanya apabila masa, hasil dan bekalan jangka panjang berada dalam talian.

Jadual Kandungan

- Garis besar

- Mengapa Keputusan Chip IC Mencipta Hasil Yang Besar

- Perkara yang diliputi oleh "IC Cip" dalam Projek Sebenar

- Titik Sakit Pelanggan dan Perkara Yang Biasanya Membetulkannya

- Senarai Semak Pemilihan IC Cip Yang Menghalang Kerja Semula

- Integrasi Ke PCBA Tanpa Kejutan Hasil

- Kawalan Kualiti dan Kebolehpercayaan Yang Sebenarnya Penting

- Kos dan Strategi Rantaian Bekalan Tanpa Mengkompromi Keselamatan

- Soalan Lazim

- Langkah Seterusnya

Garis besar

- Tentukan maksud "IC Cip" merentas fungsi, pakej dan risiko kitaran hayat

- Petakan mod kegagalan biasa kepada langkah pencegahan khusus

- Gunakan senarai semak pilihan yang meliputi kekangan elektrik, mekanikal, alam sekitar dan pembuatan

- Sepadukan IC dengan susun atur, pemasangan, pengaturcaraan dan ujian dalam fikiran

- Gunakan pengesahan praktikal dan kawalan kebolehpercayaan daripada prototaip melalui pengeluaran besar-besaran

- Imbangkan kos dan masa utama dengan pelan untuk sumber kedua dan kawalan perubahan

Mengapa Keputusan Chip IC Mencipta Hasil Yang Besar

Pasukan biasanya memilih aIC cipberdasarkan perbandingan pantas: "Adakah ia memenuhi spesifikasi dan menepati belanjawan?" Itu adalah permulaan yang baik—tetapi ia tidak mencukupi apabila anda membina sesuatu yang mesti bertahan dalam penghantaran, perubahan suhu, peristiwa ESD, kitaran tugas yang panjang dan pengguna sebenar melakukan perkara yang tidak dapat diramalkan.

Dalam amalan, IC "betul" di atas kertas masih boleh menimbulkan masalah:

- Jadual risikodari masa memimpin yang panjang atau kekurangan mendadak

- Kerugian hasildaripada kepekaan pemasangan, isu lembapan atau tapak kaki marginal

- Kegagalan lapangandaripada tegasan haba, ESD atau integriti kuasa sempadan

- Kesakitan kelayakan semulaapabila bahagian diganti tanpa kawalan yang betul

Matlamatnya bukanlah kesempurnaan—ia adalah kebolehramalan. Anda mahu aIC cipstrategi yang memastikan kejuruteraan, pembuatan dan rantaian bekalan sejajar supaya produk anda kekal stabil daripada prototaip kepada pengeluaran.

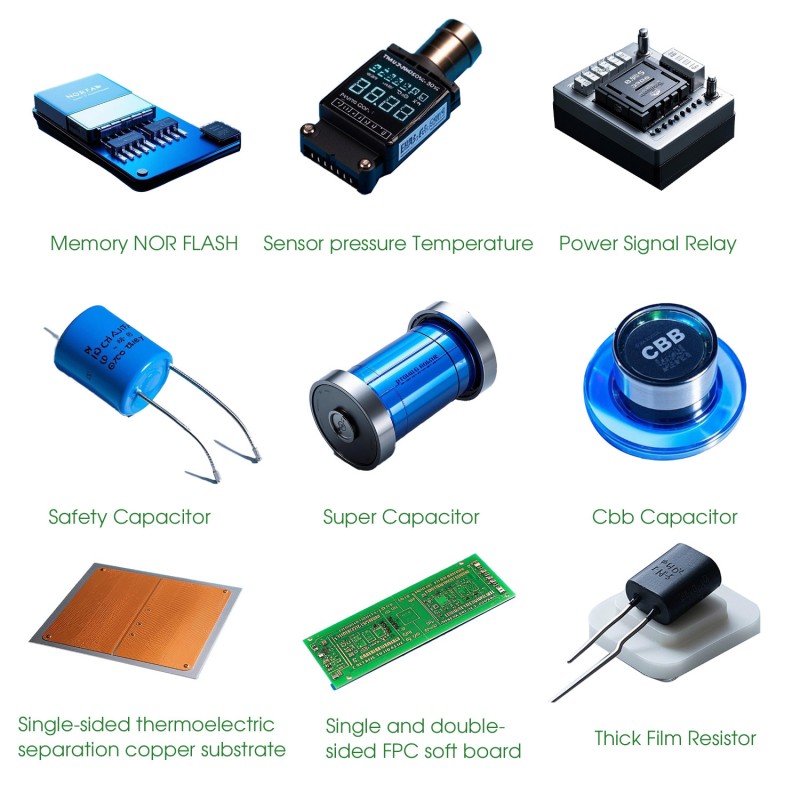

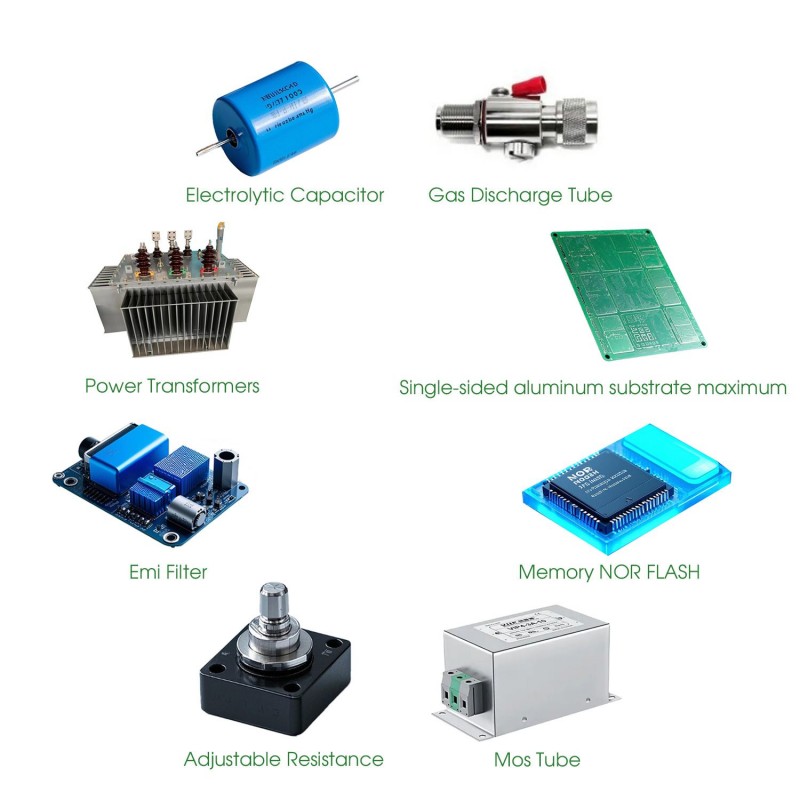

Perkara yang diliputi oleh "IC Cip" dalam Projek Sebenar

“IC cip” ialah payung yang luas dan praktikal. Bergantung pada produk anda, ia boleh merujuk kepada:

- MCU dan pemproses(logik kawalan, perisian tegar, tindanan sambungan)

- IC kuasa(PMIC, penukar DC-DC, LDO, pengurusan bateri)

- IC analog dan isyarat campuran(ADC/DAC, op-amp, antara muka penderia)

- IC antara muka dan perlindungan(USB, CAN, RS-485, tatasusunan perlindungan ESD)

- Memori dan penyimpanan(Denyar, EEPROM, DRAM)

Dua IC boleh berkongsi nombor lembaran data yang serupa dan masih berkelakuan berbeza dalam papan anda kerana jenis pakej, laluan terma, kestabilan gelung kawalan, kepekaan reka letak atau keperluan pengaturcaraan/ujian. Itulah sebabnya "memenuhi spesifikasi" hanya satu lapisan keputusan.

Titik Sakit Pelanggan dan Perkara Yang Biasanya Membetulkannya

Berikut ialah isu yang paling kerap diutarakan oleh pelanggan apabila aIC cipmenjadi halangan—dan pembaikan yang sebenarnya mengurangkan risiko.

-

Titik sakit 1: "Kami tidak boleh mendapatkan IC yang tepat dengan pasti."

Betulkan: tentukan senarai ganti yang diluluskan lebih awal, kunci proses kawalan perubahan dan sahkan alternatif dengan pelan ujian elektrik + berfungsi yang ketat. -

Pain point 2: "Prototaip kami berfungsi, tetapi hasil pengeluaran tidak stabil."

Betulkan: semak semula kekangan jejak dan pemasangan (stensil, tampal, profil aliran semula, pengendalian MSL), kemudian tambah ujian sempadan yang menangkap gelagat marginal. -

Titik kesakitan 3: "Kami bimbang tentang komponen palsu atau tebus guna."

Betulkan: laksanakan aliran kerja pengesahan masuk (kebolehkesanan, pemeriksaan visual, pemeriksaan penandaan, ujian elektrik sampel) dan gunakan saluran perolehan terkawal. -

Titik sakit 4: "Isu kuasa muncul di bawah beban atau suhu."

Betulkan: merawat integriti kuasa dan haba sebagai keperluan kelas pertama; mengesahkan sudut terburuk, bukan hanya keadaan biasa. -

Pain point 5: "Kami kehilangan masa untuk membangkitkan dan menyahpepijat."

Betulkan: reka bentuk untuk ujian (titik ujian, imbasan sempadan jika berkenaan) dan rancangan pengaturcaraan/pemuatan perisian tegar sebagai sebahagian daripada pembuatan—bukannya difikirkan semula.

Banyak pasukan yang mahukan rakan kongsi tunggal menyelaraskan sokongan pemilihan, penyepaduan PCBA, disiplin sumber dan ujian pengeluaran bekerja denganShenzhen Greeting Electronics Co., Ltd.kerana ia mengurangkan jurang penyerahan—di mana kebanyakan "kegagalan mengejut" cenderung bersembunyi.

Senarai Semak Pemilihan IC Cip Yang Menghalang Kerja Semula

Gunakan senarai semak ini sebelum anda mengunciIC cipke dalam reka bentuk anda. Ia direka untuk menangkap masalah yang tidak muncul dalam skim lembaran data pantas.

- Margin elektrik:sahkan tindanan voltan, arus, suhu dan toleransi kes terburuk—kemudian tambahkan margin untuk tingkah laku beban sebenar.

- Kesesuaian pakej dan pemasangan:mengesahkan ketersediaan pakej (QFN/BGA/SOIC, dsb.), keteguhan jejak, dan sama ada pemasang anda boleh mengendalikan keperluan padang dan pad haba.

- Laluan terma:nilai suhu simpang pada kes paling teruk dan sahkan anda mempunyai laluan haba yang realistik (tuang tembaga, vias, andaian aliran udara).

- ESD dan pendedahan sementara:petakan pendedahan dunia sebenar (kabel, sentuhan pengguna, beban induktif) dan tentukan sama ada anda memerlukan IC perlindungan luaran atau penapisan.

- Keperluan perisian tegar/pengaturcaraan:mengesahkan antara muka pengaturcaraan, keperluan keselamatan, dan sama ada pengaturcaraan pengeluaran akan dilakukan dalam talian atau luar talian.

- Kebolehujian:tentukan perkara yang anda akan ukur dalam pengeluaran (rel kuasa, bentuk gelombang utama, jabat tangan komunikasi, pemeriksaan sensor) dan pastikan papan menyokongnya.

- Risiko kitaran hayat:semak jangkaan jangka hayat dan buat rancangan untuk pembelian alternatif dan kali terakhir jika perlu.

- Disiplin dokumentasi:bekukan nombor bahagian, varian pakej dan peraturan semakan supaya penggantian tidak menjadi kegagalan senyap.

Jika anda hanya melakukan satu perkara daripada senarai ini, lakukan ini: tuliskan "tidak boleh dirunding" untukIC cip(julat elektrik, pakej, jangkaan kelayakan, kaedah pengaturcaraan) dan buat setiap alternatif membuktikan ia boleh memenuhinya.

Integrasi Ke PCBA Tanpa Kejutan Hasil

A IC ciptidak gagal secara berasingan—ia gagal dalam papan, di dalam kandang, dalam proses pembuatan sebenar. Integrasi ialah apabila kebolehpercayaan diperolehi atau hilang.

- Reka letak lebih penting daripada yang anda mahukan:IC sensitif (kelajuan tinggi, kuasa pensuisan, RF) boleh "betul" tetapi tidak stabil jika penghalaan, pembumian atau penyahgandingan adalah ceroboh.

- Penyahgandingan bukan hiasan:letakkan kapasitor seperti yang dimaksudkan, kurangkan kawasan gelung, dan sahkan tindak balas riak dan sementara di bawah beban kes terburuk.

- Reflow dan pengendalian MSL:bungkusan sensitif lembapan boleh retak atau delaminat jika peraturan penyimpanan dan pembakaran tidak dipatuhi.

- Cetakan stensil dan tampal:pakej nada halus dan pad terma memerlukan kawalan tampal untuk mengelakkan batu nisan, penyambungan atau lompang.

- Aliran pengaturcaraan:rancang akses lekapan dan tentukan cara anda mengesahkan versi dan konfigurasi perisian tegar pada penghujung baris.

Tabiat yang baik ialah melayan larian perintis pertama anda seperti percubaan pembelajaran. Jejaki jenis kecacatan, lokasi dan keadaan, kemudian tutup gelung dengan tweak reka letak atau kemas kini proses sebelum menskalakan volum.

Kawalan Kualiti dan Kebolehpercayaan Yang Sebenarnya Penting

Kebolehpercayaan bukan getaran. Ia adalah satu set semakan yang menangkap mod kegagalan yang paling mungkin anda lihat di lapangan. Jadual di bawah ialah menu praktikal—pilih yang sepadan dengan profil risiko produk anda.

| Kawalan | Apa yang Ditangkapnya | Perlaksanaan Praktikal |

|---|---|---|

| Pengesahan masuk (persampelan) | Palsu, salah varian, remarking | Pemeriksaan kebolehkesanan + pemeriksaan visual + ujian ID elektrik asas |

| Ujian margin rel kuasa | Brownouts, pengawal selia tidak stabil, beban sementara | Uji pada input min/maks, beban maks, sudut suhu |

| Rendaman haba / bakar-dalam (mengikut keperluan) | Kegagalan awal hayat, sambungan pateri marginal | Jalankan ujian berfungsi di bawah haba untuk tempoh tertentu |

| ESD/pengesahan sementara | Kegagalan sentuhan pengguna, acara kabel, sogokan induktif | Gunakan peristiwa realistik pada I/O dan sahkan tiada selak atau set semula |

| Pengesahan perisian tegar/konfigurasi | Perisian tegar yang salah, konfigurasi wilayah yang salah, penentukuran terlepas | Bacaan balik akhir baris + pengelogan versi + peraturan lulus/gagal |

Jika produk anda dihantar ke persekitaran yang keras, utamakan pengesahan haba dan sementara. Jika produk anda dihantar pada volum yang tinggi, utamakan kebolehujian dan pengesahan masuk supaya kecacatan tidak berganda merentas kelompok.

Kos dan Strategi Rantaian Bekalan Tanpa Mengkompromi Keselamatan

Kawalan kos adalah nyata—dan perlu. Tetapi pemotongan kos sekitar aIC cipboleh memperkenalkan risiko secara senyap-senyap jika ia menghilangkan kebolehkesanan, melemahkan cek masuk, atau menggalakkan penggantian yang tidak terkawal.

- Tentukan "penggantian yang dibenarkan" secara bertulis:gred elektrik yang sama, pakej yang sama, jangkaan kelayakan yang sama. Perkara lain mencetuskan pengesahan semula.

- Gunakan pelan penyumberan dua lapisan:saluran utama untuk kestabilan; sekunder untuk kontingensi—kedua-duanya disemak dan boleh dikesan.

- Pastikan selang seli hangat:jangan tunggu sehingga berlaku kekurangan. Bina kumpulan kecil dengan alternatif dan jalankan ujian penerimaan anda sekarang.

- Track lot dan kod tarikh:ia membantu anda mengasingkan isu dengan cepat jika gugusan kecacatan muncul.

- Rancang untuk acara kitaran hayat:jika IC berkemungkinan tamat tempoh dalam tetingkap sokongan produk anda, reka bentuk dalam laluan migrasi lebih awal.

Cara praktikal untuk kekal waras ialah menyambungkan peraturan kejuruteraan (apa yang boleh diterima) dengan peraturan pembelian (apa yang dibenarkan untuk dibeli) supaya sistem tidak hanyut di bawah tekanan tarikh akhir.

Soalan Lazim

S: Apakah yang perlu saya sahkan dahulu apabila memilih IC Cip?

A:Mulakan dengan margin elektrik terburuk dan kesesuaian pakej/pengilangan. Jika IC tidak boleh dipasang dengan pasti atau ia menjadi panas pada beban terburuk anda, segala-galanya menjadi kawalan kerosakan.

S: Bagaimanakah cara saya mengurangkan risiko IC Cip palsu?

A:Memerlukan kebolehkesanan, elakkan pembelian tempat yang tidak terkawal dan tambah pemeriksaan pensampelan masuk (penandaan, pembungkusan dan pengesahan elektrik yang cepat). Untuk binaan berisiko lebih tinggi, tingkatkan saiz sampel dan hasil log dengan lot.

S: Mengapakah IC kuasa saya berkelakuan berbeza pada papan akhir berbanding pada papan eval?

A:Reka letak, pembumian dan peletakan komponen sering mengubah gelagat kawalan dan persekitaran hingar. Sahkan dengan PCB tepat anda, profil beban tepat anda, dan pendawaian/kabel sebenar anda.

S: Adakah saya memerlukan burn-in untuk setiap produk?

A:Bukan selalu. Burn-in adalah paling berguna apabila kegagalan awal hayat akan mahal, apabila akses medan sukar, atau apabila anda melihat kecacatan kecil dalam larian perintis. Jika tidak, ujian berfungsi yang kukuh dan pengesahan masuk mungkin lebih cekap.

S: Bagaimanakah saya boleh mengelakkan kelewatan yang disebabkan oleh masa pendahuluan IC?

A:Kunci silih berganti awal, sahkannya sebelum anda terpaksa bertukar, dan pastikan peraturan pembelian anda sejajar dengan senarai diluluskan kejuruteraan supaya penggantian tidak berlaku secara senyap.

S: Apakah yang menjadikan IC Cip "sedia pengeluaran"?

A:Ia bukan sahaja tentang lulus demo prototaip. Sedia pengeluaran bermakna IC boleh diperolehi dengan kebolehkesanan, dipasang dengan hasil yang stabil, lulus ujian akhir talian yang konsisten dan tahan di bawah keadaan persekitaran dan sementara anda.

Langkah Seterusnya

Jika anda mahukan andaIC cipkeputusan untuk berhenti menjadi perjudian, menganggap pemilihan, penyumberan, pemasangan dan ujian sebagai satu sistem yang bersambung. Begitulah cara anda menghalang gelung klasik "kejayaan prototaip → kejutan perintis → kelewatan pengeluaran."

PadaShenzhen Greeting Electronics Co., Ltd., kami membantu pasukan mengubah ketidakpastian IC Chip kepada pelan terkawal—daripada sokongan pemilihan dan penyepaduan PCBA kepada aliran kerja pengesahan dan ujian pengeluaran. Jika anda menghadapi kekurangan, ketidakstabilan hasil atau kebimbangan kebolehpercayaan, beritahu kami aplikasi, persekitaran sasaran dan volum anda, dan kami akan mencadangkan laluan praktikal ke hadapan.

Bersedia untuk bergerak lebih pantas dengan risiko yang kurang?Kongsi BOM dan keperluan anda dan hubungi kami untuk membincangkan strategi Chip IC dan PCBA yang boleh dipercayai yang disesuaikan dengan produk anda.